Laboratory Facilities

Our signal processing lab offers a variety of resources including a wide range of state-of-the-art test and measurement hardware as well as a stock of standard active and passive electronic components that extends into the radio frequency (RF) range.Present and past projects include:

Compressed Sensing Radar

The aim of this project is a hardware implementation of a compressed sensing radar system. The setup consists of RF instruments to generate RF probing signals and to capture the corresponding responses delivered by a hardware channel emulator.

The aim of this project is a hardware implementation of a compressed sensing radar system. The setup consists of RF instruments to generate RF probing signals and to capture the corresponding responses delivered by a hardware channel emulator.The problem of identifying the delay-Doppler shifts induced by the targets can be reduced to that of recovering a sparse vector from (highly) undersampled measurements. Standard approaches to solving the corresponding problem include ℓ1-minimization or greedy algorithms such as orthogonal matching pursuit. It was shown recently in [1] that recovery of the delay-Doppler shifts in the radar and the (more general) system identification problem can also be formulated as the recovery of a sparse vector from multiple measurements (MMV problem). The MMV recovery problem can be solved efficiently using low-complexity subspace algorithms such as, e.g. MUSIC or ESPRIT.

These subspace algorithms are implemented in MATLAB and on an FPGA. The final goal is a VLSI implementation.

Reference:

[1] R. Heckel and H. Bölcskei, "Identification of sparse linear operators," IEEE Transactions on Information Theory, Vol. 59, No. 12, pp. 7985-8000, Dec. 2013. [Link to document]

Practical Applications of Compressed Sensing

Compressed Sensing (CS) is a way of acquiring sparse signals (e.g. images) at a sampling rate significantly lower than the Nyquist rate while still allowing to accurately reconstruct the signals. In two hardware projects, we build prototypes that allow us to exploit these ideas for practical applications in different fields such as object tracking in a light curtain and indoor localization using LED lighting. The projects are carried out in collaboration with the Telecommunications Circuits Lab (TCL) at EPFL.

Compressed Sensing (CS) is a way of acquiring sparse signals (e.g. images) at a sampling rate significantly lower than the Nyquist rate while still allowing to accurately reconstruct the signals. In two hardware projects, we build prototypes that allow us to exploit these ideas for practical applications in different fields such as object tracking in a light curtain and indoor localization using LED lighting. The projects are carried out in collaboration with the Telecommunications Circuits Lab (TCL) at EPFL.

Relaying and Interference Alignment Testbed

The nodes developed for the real-time MIMO testbed described below are also used, with some modifications, in our relaying and interference alignment (IA) testbed. The practical implementation of different relaying protocols

with the aim of demonstrating the feasibility of cooperative diversity concepts and the idea of network crystallization allows us to gain valuable insights into practical problems associated with these ideas.

Specifically, issues such as efficient distribution of channel state information, data sharing, frequency offset correction, and

synchronization can be analyzed in this flexible testbed environment.

The testbed is also used to understand the practical performance limitations of different interference alignment concepts, such as number-theoretic IA, ergodic IA, topological IA, and blind IA.

The nodes developed for the real-time MIMO testbed described below are also used, with some modifications, in our relaying and interference alignment (IA) testbed. The practical implementation of different relaying protocols

with the aim of demonstrating the feasibility of cooperative diversity concepts and the idea of network crystallization allows us to gain valuable insights into practical problems associated with these ideas.

Specifically, issues such as efficient distribution of channel state information, data sharing, frequency offset correction, and

synchronization can be analyzed in this flexible testbed environment.

The testbed is also used to understand the practical performance limitations of different interference alignment concepts, such as number-theoretic IA, ergodic IA, topological IA, and blind IA.

Real-Time MIMO Hardware Testbed (completed project)

The implementation of algorithms in hardware helps not only in the validation of

theoretical ideas, but also in demonstrating their practicality, and in identifying new research problems.

While our research mostly concentrates on theoretical developments, system analysis and simulation, we have a strong interest in

hardware development and practical implementations of novel algorithms. To this end, we collaborate closely with the IIS at ETH Zurich.

The implementation of algorithms in hardware helps not only in the validation of

theoretical ideas, but also in demonstrating their practicality, and in identifying new research problems.

While our research mostly concentrates on theoretical developments, system analysis and simulation, we have a strong interest in

hardware development and practical implementations of novel algorithms. To this end, we collaborate closely with the IIS at ETH Zurich.

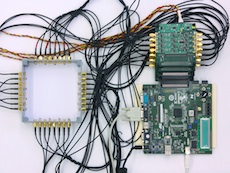

A broadband multiuser MIMO hardware testbed forms the core for our implementations. Each modem has 4x4 MIMO capability at a bandwidth of up to 40 MHz and at carrier frequencies of up to 6 GHz.

The testbed architecture is based on programmable hardware (FPGAs) with custom RF front-ends. The physical layer is based on the IEEE 802.11n specifications, and the real-time MIMO baseband processing algorithms are implemented and tested on powerful generic Multi-FPGA signal processing hardware.

The hardware was developed entirely in-house.